我的世界随机储存器原理及搭建教程

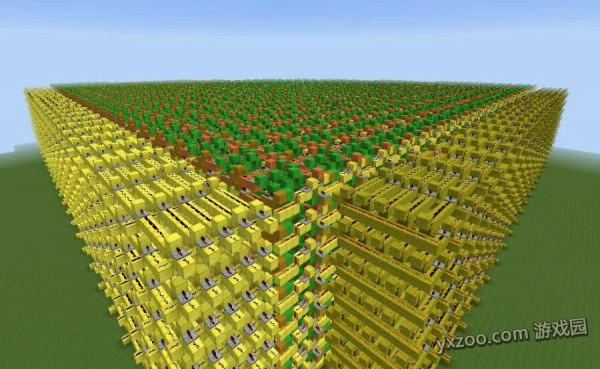

在游戏中实现真实世界中的计算机硬件系统,听上去似乎是不太可能的,不过我的世界这一款这么神奇的游戏就实现了!今天游戏园小编为大家带来了我的世界随机存储器的组成原理4及搭建教程,希望大家能够喜欢!

一、RAM基础理论知识

1.RAM概述

RAM是英文Random Access Memory的缩写,中文即随机存取存储器,可以存储二进制代码,具有可读可写、且存取的速度与存储单元的位置无关的特性。在计算机中,RAM也叫主存(或内存),是与CPU直接交换数据的内部存储器,需要进行传输的数据就存放在内存中。

2.RAM的技术指标

(1).存储容量

RAM的容量是指能储存二进制代码的数量,由存储单元的数量决定,每个存储器又包含多个存储元件(又叫存储基元、存储元)。每个存储元件能存储一位二进制码0或1,每个存储单元能存储一串二进制码,称为一个存储字,存储字的位数叫存储字长,存储字长可以为8位、16位等。容量(Byte)=存储单元数量*字长/8。

(2).存储速度

RAM的速度主要由频率、位宽(频率*位宽=带宽,即单位时间传输数据量)、延迟(又称时序)决定,具体是由存储时间和存储周期决定。

存储时间又叫访问时间(Memory Access Time),指启动一次操作到完成这次操作所有过程所需要的时间。

存储周期(Memory Cycle Time),是指连续完成两次独立操作的最小间隔时间,这个间隔时间通常大于或者等于存储时间。

(3).存储密度

RAM的存储密度=容量/体积(或面积),主要由存储单元体积和布线决定,存储单元体积越小布线越紧密在单位体积内就可以集成更多的存储单元,获得更大的容量。

3.RAM的基本组成结构以及工作方式

(1).RAM的基本结构

RAM的基本结构包括MAR(Memory Address Register,内存地址寄存器)、译码器(Address Decoder)、驱动器(Device)、存储体、控制电路、读写电路、MDR(Memory Data Register,内存数据寄存器),(有的将MAR和MDR集成于CPU中),MAR用于储存地址,译码器负责地址译码,驱动器负责驱动电路,存储体负责储存数据,控制电路用来控制读取或写入,读写电路负责实现读写控制,MDR用来储存从存储体读取的数据或者准备写入存储体的数据。

(2).RAM的工作过程

内存的工作方式是按地址访问存储单元,每个存储单元都有一个对应的地址,当要对内存进行操作时,首先由CPU将要操作的存储单元的地址送入MAR,经地址总线(Address Bus)送至内存的译码器进行解码,驱动电路选中对应的存储单元,然后CPU发出读写操作指令,内存将存储单元里的数据取出经数据总线(Data Bus)存至MDR里,或者是将MDR里的数据写入存储单元。

(3).RAM的电路结构

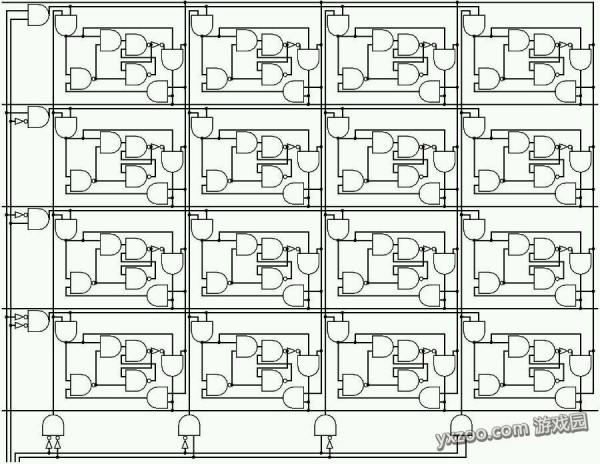

这是一个使用D触发器进行存储,重合法译码驱动,读写控制线控制读写的RAM,包含16个1bit存储元。最上方的是读写控制线,左下方的是地址线,中间四根是数据线,低电平控制读取,高电平控制写入,读写共享同一根数据线。

该RAM使用SR Latch作为存储基元,译码驱动为线选法,由时钟控制,含4个4bit存储单元。左边是一根时钟线和两根地址线,上面四根线为数据输入(Data in),下面四根线为数据输出(Data out)。

在游戏中实现真实世界中的计算机硬件系统,听上去似乎是不太可能的,不过我的世界这一款这么神奇的游戏就实现了!今天游戏园小编为大家带来了我的世界随机存储器的组成原理4及搭建教程,希望大家能够喜欢!

一、RAM基础理论知识

1.RAM概述

RAM是英文Random Access Memory的缩写,中文即随机存取存储器,可以存储二进制代码,具有可读可写、且存取的速度与存储单元的位置无关的特性。在计算机中,RAM也叫主存(或内存),是与CPU直接交换数据的内部存储器,需要进行传输的数据就存放在内存中。

2.RAM的技术指标

(1).存储容量

RAM的容量是指能储存二进制代码的数量,由存储单元的数量决定,每个存储器又包含多个存储元件(又叫存储基元、存储元)。每个存储元件能存储一位二进制码0或1,每个存储单元能存储一串二进制码,称为一个存储字,存储字的位数叫存储字长,存储字长可以为8位、16位等。容量(Byte)=存储单元数量*字长/8。

(2).存储速度

RAM的速度主要由频率、位宽(频率*位宽=带宽,即单位时间传输数据量)、延迟(又称时序)决定,具体是由存储时间和存储周期决定。

存储时间又叫访问时间(Memory Access Time),指启动一次操作到完成这次操作所有过程所需要的时间。

存储周期(Memory Cycle Time),是指连续完成两次独立操作的最小间隔时间,这个间隔时间通常大于或者等于存储时间。

(3).存储密度

RAM的存储密度=容量/体积(或面积),主要由存储单元体积和布线决定,存储单元体积越小布线越紧密在单位体积内就可以集成更多的存储单元,获得更大的容量。

3.RAM的基本组成结构以及工作方式

(1).RAM的基本结构

RAM的基本结构包括MAR(Memory Address Register,内存地址寄存器)、译码器(Address Decoder)、驱动器(Device)、存储体、控制电路、读写电路、MDR(Memory Data Register,内存数据寄存器),(有的将MAR和MDR集成于CPU中),MAR用于储存地址,译码器负责地址译码,驱动器负责驱动电路,存储体负责储存数据,控制电路用来控制读取或写入,读写电路负责实现读写控制,MDR用来储存从存储体读取的数据或者准备写入存储体的数据。

(2).RAM的工作过程

内存的工作方式是按地址访问存储单元,每个存储单元都有一个对应的地址,当要对内存进行操作时,首先由CPU将要操作的存储单元的地址送入MAR,经地址总线(Address Bus)送至内存的译码器进行解码,驱动电路选中对应的存储单元,然后CPU发出读写操作指令,内存将存储单元里的数据取出经数据总线(Data Bus)存至MDR里,或者是将MDR里的数据写入存储单元。

(3).RAM的电路结构

这是一个使用D触发器进行存储,重合法译码驱动,读写控制线控制读写的RAM,包含16个1bit存储元。最上方的是读写控制线,左下方的是地址线,中间四根是数据线,低电平控制读取,高电平控制写入,读写共享同一根数据线。

该RAM使用SR Latch作为存储基元,译码驱动为线选法,由时钟控制,含4个4bit存储单元。左边是一根时钟线和两根地址线,上面四根线为数据输入(Data in),下面四根线为数据输出(Data out)。

4.RAM的储存原理

(1).SRAM

SRAM即Static Random Access Memory静态随机存储器,是在静态触发器的基础上附加门控管而构成的,在读取数据后仍保持原状态,不需要再生。

(2).DRAM

DRAM即Dynamic Random Access Memory动态随机存储器,存储矩阵由动态MOS存储单元组成,利用MOS管的栅极电容来储存信息,但由于栅极电容的容量很小,电荷的保存时间有限,必须定时补充电荷保持信息,即“刷新”或者“再生”,因此DRAM内部需要有刷新控制电路。

5.RAM的译码驱动方式

存储芯片的译码驱动方式主要有两种,线选法和重合法。

(1).线选法

线选法的特点是一根字选择线(Word Line,字线)直接选中一个存储单元的各个位,如直接选中8个1bit存储元件组成1Byte存储单元,这样便可以一次控制一个字,这种方法结构相对简单,但只适合容量不大的存储芯片。

(2).重合法

重合法的特点是利用行地址和列地址确定位置,两组线相互交叉,一组选择行,一组选择列,即可控制存储矩阵的任意一位。

6.RAM的容量扩展方式

由于单片存储芯片的容量总是有限的,为了满足应用需求,需将多片存储芯片组合在一起组成容量足够的存储器,这就是存储容量的扩展。容量控制的方式通常有两种,位扩展和字扩展。

(1).位扩展

位扩展是指增加存储字长,将多片存储芯片并联,由原来的一次控制一个存储芯片的

一个字变成一次控制各个芯片的一个字,这样一次便控制了更长的字,同时容量也获得了扩展。

(2).字扩展

字扩展是指增加存储器字的数量,通过增加多个存储芯片,增加几位信号作为片选信号,通过片选器来选择对应的存储芯片,这样可以扩展存储容量而不改变存储字长。

(3).字、位扩展

增加存储芯片数量,且既增加存储的字的数量同时又扩展存储字长。

二、红石电路RAM基础

1.数字电路与信号强度电路

(1).数字电路

数字电路由红石火把、中继器等组成,通过有信号和无信号来表示1和0,对应物理电路中的高电平和低电平,以红石火把加方块组成反相器构成各种逻辑门,进而组成数字逻辑电路。

(2).信号强度电路

信号强度电路又称为模电,信号强度在零到十五的称为普通模电,信号强度高于十六的为高强度模电,简称强模。强度信号需要进行保真传输,红石线承载的红石信号强度范围为0~15,比较器储存和传递任意强度的信号,因此传输上可以使用红石线的普通模电延迟相对较小,强模信号只能使用比较器链进行传输,延迟相对较大,但值的范围更大。因为利用信号强度来表示一定的值,所以相比相同位数的数字电路数据量更大。

2.存储元件

存储元件基于锁存器构成,除了满足基本的存储功能以外还应具有易于扩展堆叠、高度集成等特点,以方便电路的制作。

(1).传统锁存器

传统锁存器即普通的双与非门锁存器,在红石电路中可由两个首尾相连的非门构成,包括红石火把非门构成的锁存器和活塞非门构成的锁存器。

为了方便存储矩阵的制作,通常一个存储单元还包含字线、位线、读写控制线、数据线等,形状规则,方便复制拼接等。

3.译码器

(1).数电译码器

即基于数字信号的译码器,由BIN信号转换为其它信号进行存储单元选择的译码器,常见的有2-4译码器、3-8译码器、4-16译码器等,由与门或门蕴含门等构成。

(2).模电译码器

利用红石信号的强度表示地址,译码过程中将信号强度转换为数电信号,利用比较器的比较功能或者减法功能或者构建蕴含门来区分信号,通常用普通模电,体积较小,且速度也比较快,但有间距限制,也只适合容量较小的存储器。

三、搭建红石RAM

1.设定目标

确定RAM需要达到的容量、体积、延迟等指标,根据指标进行RAM的规划。

2.选择译码驱动方式

容量较小的RAM可以使用线选法驱动,结构简单任意实现;大容量的RAM使用重合法驱动,通常重合法一个存储芯片只有1bit位宽,需要通过位控制达到所需存储字长。

3.考虑电路结构

线选法由于存储字长的限制结构也受到限制,通常使用并列的单片式触发器组成一个存储单元,根据存储单元的形状来规划电路,通常将存储单元布置在译码器和数据线的一侧或两边都布置;重合法相对要单一一些,一般是将行地址译码器和列地址译码器布置在存储矩阵的相邻的两边。

4.搭建存储基元

基于线选法的RAM一般使用单片式的触发器,将8或16个触发器并列组成一个8bit或16bit的存储单元,可以组成1宽的存储单元或者方形的存储单元,在存储单元输入输出口搭建读写控制电路;重合法使用扁平的矩形存储基元,每个存储基元都需要有对应的控制电路,由一个触发器加上驱动线、读写控制线、数据线组成一个扁平的存储基元,以方便拼接组成存储矩阵和纵向堆叠。搭建完成以后进行测试以保证能够正常工作。

5.完成存储体

线选法的RAM可以先搭建一个包含一个存储单元和一段译码器一段数据线一段控制线的基本结构,然后使用WorldEdit或者MCEdit对其进行复制从而构建整个存储体;重合法的RAM只需直接复制基本单元构成存储矩阵即可。

6.RAM完成

将地址线数据线读写控制线拉出布置到指定位置,完成译码器的地址分配。检查电路确认是否存在断路或者短路问题,测试RAM的读写功能,确认译码器和读写控制电路是否能正常工作,清除多余的部分。

精品推荐

相关文章

更多+热门搜索

手游排行榜

- 最新排行

- 最热排行

- 评分最高

-

冒险解谜 大小:143MB

-

飞行射击 大小:355.07MB

-

休闲益智 大小:19.6M

-

图像影音 大小:475.72MB

-

赛车竞速 大小:34.63M